荊州市城市管理執法委員會

荊州市城市管理執法委員會

政府信息公開

您現在的位置:首頁

PCIe谁有财色无边全文无删减,狂飆20年

近來,PCI-SIG正式發布PCIe 8.0規范,將數據傳輸速率推高至256GT/s,再次完結帶寬翻倍,這無疑是PCIe技能開展進程中的又一里程碑。

從串行總線改造到每秒256GT的速度打破,PCIe技能用20余年時刻重構核算機數據傳輸格式。在現在的技能矩陣中,PCIe憑仗其特性優勢與共同定位,不只是銜接主板與各類擴展卡的橋梁,更在數據中心、云核算、高功能核算等范疇肩負著數據高速流通的重擔。

回憶這一開展進程,一系列值得沉思的問題閃現:

PCIe技能怎么歷經二十余載風雨洗禮,在迭代之路上一路狂飆?

PCIe在很多專用互聯技能的沖擊下,怎么占有職業中心位置?

站在技能改造的十字路口,PCIe又將怎么打破枷鎖、迭代演進,為未來核算架構拓荒全新的幻想空間?

尤其是在高速互聯技能不斷演進的當下,咱們需求深化分析PCIe的開展頭緒,及其共同定位與鴻溝,探尋其間的答案。

從PCI到PCIe,打破傳統互聯枷鎖

PCIe全稱為Peripheral Component Interconnect Express,開端由Intel在2001年提出,是一種高速串行核算機擴展總線規范,用于銜接主板和高速外圍設備,后續交由PCI-SIG(PCI特別愛好安排)認證后,該規范被命名為“PCI-Express”,簡稱“PCIe”,旨在代替舊的PCI、PCI-X和AGP總線規范。

在PCIe誕生之前,核算機首要依賴于并行總線技能進行內部數據傳輸。最具代表性的并行總線技能是PCI(Peripheral Component Interconnect)。PCI總線在1992年由Intel推出,旨在處理前期ISA和VLB總線的速度和兼容性問題。PCI總線可以支撐多個設備同享數據途徑,最大帶寬為133 MB/s,這在其時現已十分高效。

但是,跟著核算機硬件功能的不斷進步,PCI總線的約束性逐步閃現。并行傳輸辦法導致信號衰減嚴峻,時鐘同步變得困難,約束了傳輸速度的進一步進步。這些要素推進了對PCIe新式總線技能的需求。

圖源:FMS

作為現代核算渠道的中心互聯技能,PCIe憑仗串行總線架構完結了對傳統PCI并行總線的全面改造。相較于并行傳輸形式,PCIe經過三大中心特性打破了傳統技能的約束:

串行通訊機制:以串行傳輸代替并行架構,從物理層削減信號攪擾,明顯進步數據傳輸功率與有用間隔;

點對點銜接規劃:每個外設經過獨立鏈路直接對接根復合體,消除總線競賽瓶頸,完結數據傳輸的直接性與高效性;

可擴展帶寬才能:支撐經過通道(Lane)數量線性擴展帶寬,靈敏匹配不同設備的功能需求。

這些技能特性不只為顯卡、存儲設備、網卡等外設供給了遠超傳統PCI的傳輸帶寬與更低推延,更經過高效資源調度下降體系占用,成為支撐今世核算機硬件高速互聯的中心技能柱石,深刻影響著整個核算體系的架構規劃與功能優化方向。

圖源:信維智算

跟著PCIe技能的不斷開展和運用,至今已歷經多代迭代晉級,已開展為現代核算機硬件互聯的中心技能,精準適配了今世核算渠道對帶寬繼續增加的需求, 其會員公司數量截止2024年12月已達1000家。

速率狂飆20年:PCIe 1.0到8.0的迭代之路

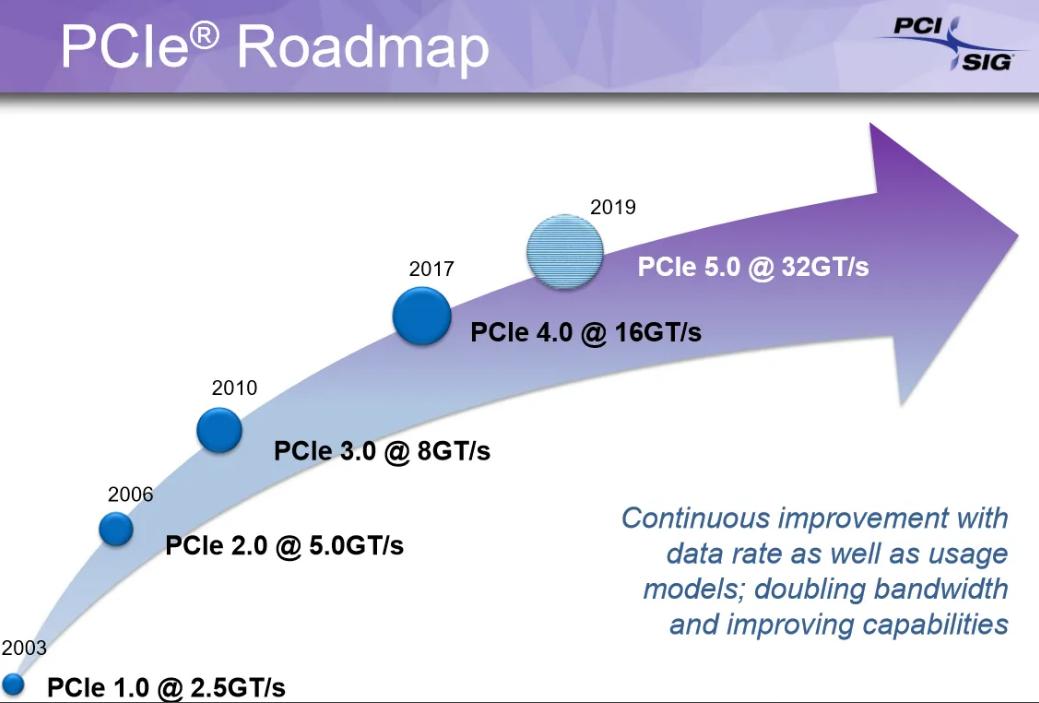

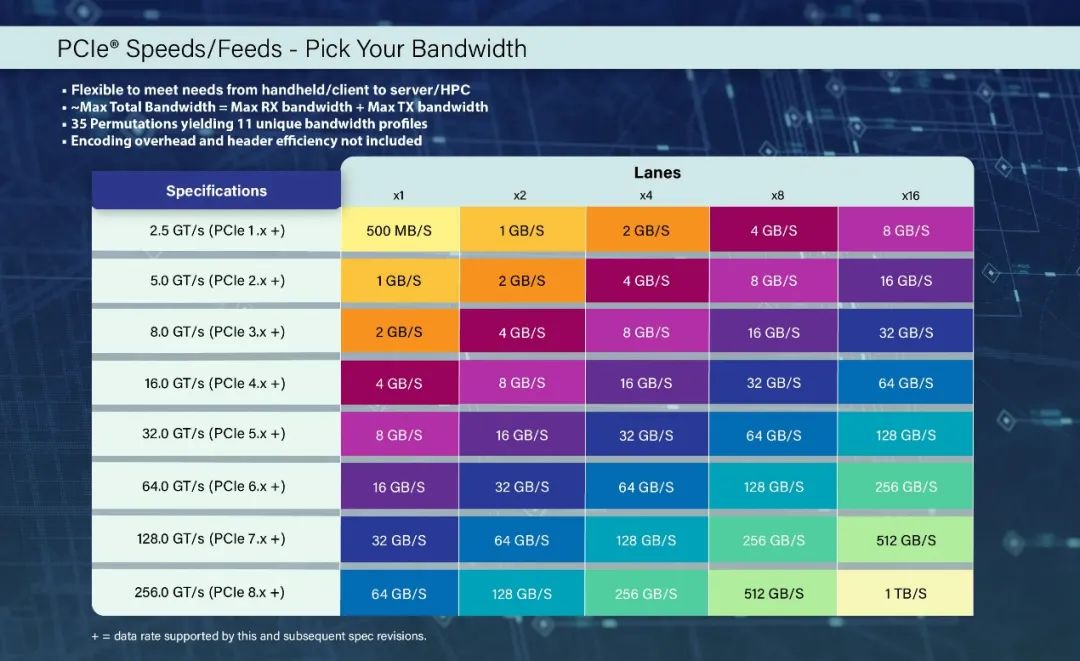

自2003年發布首個版別以來,PCIe開展至今現已從開端的1.0晉級到了8.0,閱歷了屢次重要迭代,數據傳輸速率和功能不斷進步。

首要咱們介紹一下PCIe規范的演進前史以及各代PCIe規范之間的首要差異:

PCIe 1.0:

串行互聯起點,2.5GT/s敞開總線改造

作為PCI Express技能的首個規范,PCIe 1.0于2003年由PCI-SIG正式推出,標志著從傳統PCI總線向串行互聯架構的轉型。

PCIe 1.0單通道傳輸速率為2.5GT/s,選用8b/10b編碼,單通道帶寬約250MB/s。相較于并行PCI總線,PCIe 1.0經過點對點串行鏈路規劃,大幅下降了信號攪擾,進步了數據傳輸的穩定性與功率。這一帶寬遠超PCI,總線的速度得到了明顯進步。

2005年推出的PCIe 1.1版別對規范細節進行弄清與優化,未改動中心速率,為后續迭代奠定了兼容性根底,成為前期顯卡、網卡等外設的干流銜接規范。

PCIe 2.0:速率翻倍與兼容性接連

跟著技能的前進,2007年頭PCIe 2.0正式發布。

PCIe 2.0在PCIe 1.x的根底上完結了傳輸功能的跨越式進步,每通道速率從2.5GT/s翻倍至5GT/s,單通道帶寬進步至500MB/s,x16裝備下總吞吐量達8 GB/s。

PCIe 2.0規范在技能上接連了串行鏈路架構,經過優化信號完好性規劃(如增強發射端預加劇),在堅持與前代設備徹底向后兼容的一起,滿意了高清顯卡、高速存儲等外設對帶寬增加的需求。

這一版別的遍及推進了消費電子與服務器范疇的硬件晉級,成為PCIe技能從起步走向老練的要害節點。

PCIe 3.0:

CTLE技能為高功能顯卡與SSD鋪路

2010年11月,幾經推延的PCIe 3.0規范正式發布,標志著PCIe技能進入高效傳輸新階段。該版別完結了每通道8GT/s的傳輸速率,單通道帶寬進步至約1GB/s,一起開端運用更高效的128b/130b編碼計劃來優化傳輸功率,并堅持了與PCIe 2.0在軟件及機械接口上的徹底兼容。

為支撐高頻傳輸需求,PCIe 3.0引進接納端接連時刻線性均衡(CTLE)等先進信號處理技能,合作發送器去加劇機制與接納器均衡規劃,有用補償高頻信號衰減,明顯進步了信號完好性。此外,其經過協議棧優化下降傳輸推延,并晉級電源管理機制完結精細化功耗操控,可一起滿意移動設備與數據中心的能效需求。

作為2010年代消費級與企業級硬件的干流互聯規范,PCIe 3.0為高功能顯卡、SSD等設備供給了足夠帶寬支撐,推進了核算渠道功能的全體躍升。

PCIe 4.0:解鎖NVMe SSD滿速潛能,

推進消費級商場遍及

2017年,PCIe 4.0規范面世,完結了傳輸速率的再次翻倍,每通道速率達16GT/s,單通道帶寬約2GB/s,編碼計劃接連高效的128b/130b格式。一起,技能上接連前代信號完好性優化思路,經過增強均衡算法與時鐘同步機制,合作計時器擴展通道規劃的規劃,有用優化長間隔信號傳輸穩定性,為高速率下的鏈路可靠性供給中心支撐。

作為首個全面支撐NVMe SSD滿速運轉的PCIe版別,PCIe 4.0的高帶寬才能明顯開釋了存儲功能潛力,一起為高功能核算、數據中心AI加快等場景的高帶寬需求供給了要害支撐。該規范由AMD銳龍3000系列CPU首要大規劃選用,憑仗對前代設備的徹底向后兼容性完結滑潤過渡,快速推進其在消費級與企業級商場的遍及,成為銜接SSD、GPU等高速外設的中心互聯規范。

PCIe 5.0:

三大技能改造,中心功能繼續進步

自PCIe 4.0推出后,技能迭代節奏明顯加快。

圖源:PCI-SIG

PCI-SIG于2019年5月正式發布PCIe 5.0規范,在堅持與前代技能向后兼容的根底上,完結傳輸速率的翻倍進步,到達32GT/s,單通道帶寬進步至約4GB/s,經過x16裝備可完結128GB/s的吞吐量,足以支撐數據中心400GE網絡的高速傳輸需求。

作為PCIe 4.0的擴展性晉級,PCIe 谁有财色无边全文无删减5.0接連了老練的技能結構,選用與前代相同的Tx/Rx測驗辦法及依據“眼睛”寬度和高度的接納器應力顫動校準機制,僅經過針對性的電氣優化完結功能躍升。

PCIe 5.0中心技能改造體現在三方面:

新增均衡旁路形式,支撐從 2.5 GT/s 直接切換至 32 GT/s 的鏈路練習,大幅縮短設備初始化時刻,為高速鏈路均衡測驗供給高效途徑;

經過通道裕度調整和信號均衡技能的優化,有用下降長間隔傳輸的信號丟失,進步鏈路穩定性;

在速率進步的一起完結推延下降,合作低功耗規劃,完美適配人工智能、機器學習等數據密集型作業負載的功能需求。

全體而言,PCIe 5.0的規范演進聚集于中心功能進步,僅在信號完好性增強和高速傳輸支撐等要害范疇進行針對性調整,以最小化的技能改動完結了傳輸功率的跨越式進步。

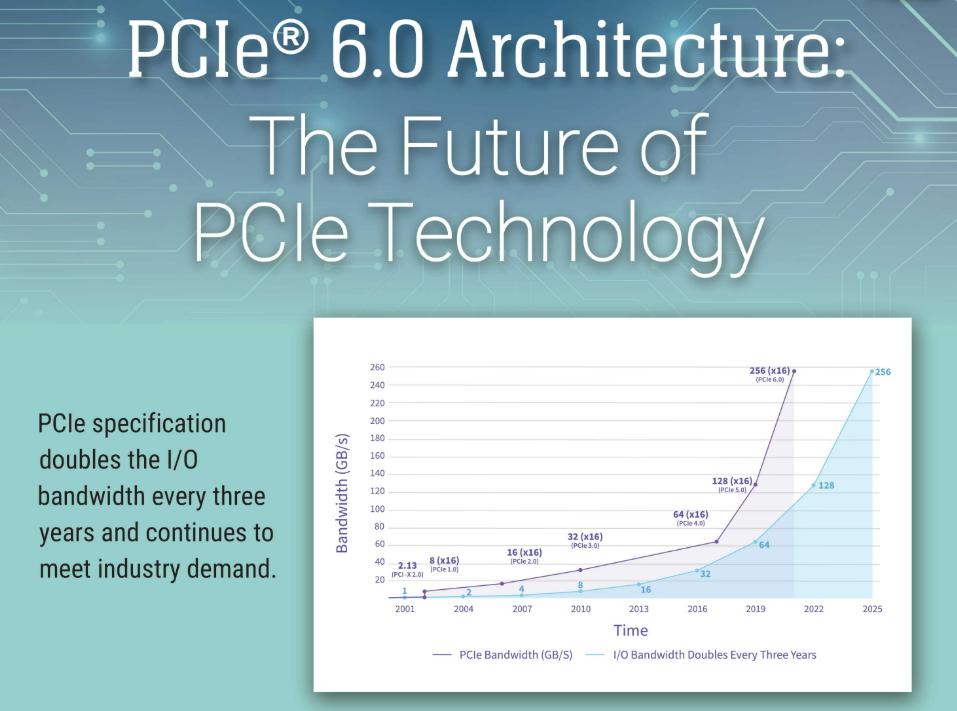

PCIe 6.0:從頭界說數據傳輸功率鴻溝

2022年1月,PCI-SIG正式發布PCIe 6.0規范,標志著高速互聯技能進入全新開展階段。

作為PCIe技能演進中的里程碑版別,PCIe 6.0初次引進脈沖幅度調制 PAM4信號編碼,在堅持信道帶寬不變的前提下,完結了傳輸速率的翻倍打破,單通道數據速率進步至64GT/s,對應單通道帶寬達8GB/s,經過x16裝備可供給256GB/s的總吞吐量,足以支撐數據中心800GE網絡的高速傳輸需求。

圖源:PCI-SIG官網

PCIe 6.0的中心技能改造體現在物理層晉級、邏輯層改造以及兼容性與可靠性等多維度的優化:

物理層晉級:選用PAM4調制技能代替傳統NRZ編碼,經過四電平信號傳輸完結相同符號率下的帶寬翻倍,一起引進前向糾錯(FEC)機制,有用補償高速傳輸中的信號損耗,保證數據完好性;

邏輯層改造:引進流量操控單元(FLIT)編碼,將數據封裝為固定巨細的256B傳輸單元,代替前代的128B/130B編碼和DLLP開支,明顯進步業務層數據包(TLP)的傳輸功率;

兼容性與可靠性:接連向后兼容規劃,一起經過Retimer信號重構、動態鏈路均衡調校等技能優化,在進步速率的一起下降推延,保證多設備在樹型拓撲中完結高效通訊。

這些技能晉級使PCIe 6.0完美適配AI練習、機器學習、云核算、超大規劃數據中心等新式場景的高帶寬需求,為5G、高端存儲、視覺核算等范疇的開展供給了中心支撐。

作為一場重構硬件通訊規矩的技能改造,PCIe 6.0以64 GT/s的高速功能,進一步穩固了其在核算機體系互聯中的中心位置,從頭界說了硬件設備間數據傳輸的功率鴻溝。

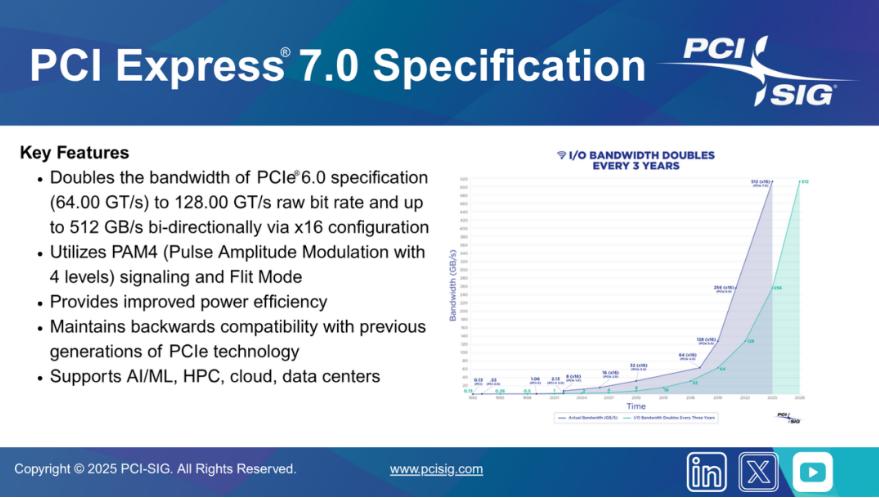

PCIe 7.0:經過光學重定時器打破傳輸約束

2024年,PCI-SIG安排現已發布了PCIe 7.0規范。

PCIe 7.0接連了歷代版別的功能躍升途徑,在PCIe 6.0根底上完結帶寬翻倍,每通道傳輸速率進步至128GT/s,x16通道雙向帶寬可達512GB/s,單通道帶寬約16GB/s,進一步滿意數據中心與AI運用的極致功能需求。

圖源:PCI-SIG官網

技能上,PCIe 7.0沿襲PCIe 6.0的PAM4調制與FLIT形式下的1b/1b編碼計劃,并堅持對前代規范的向下兼容性。

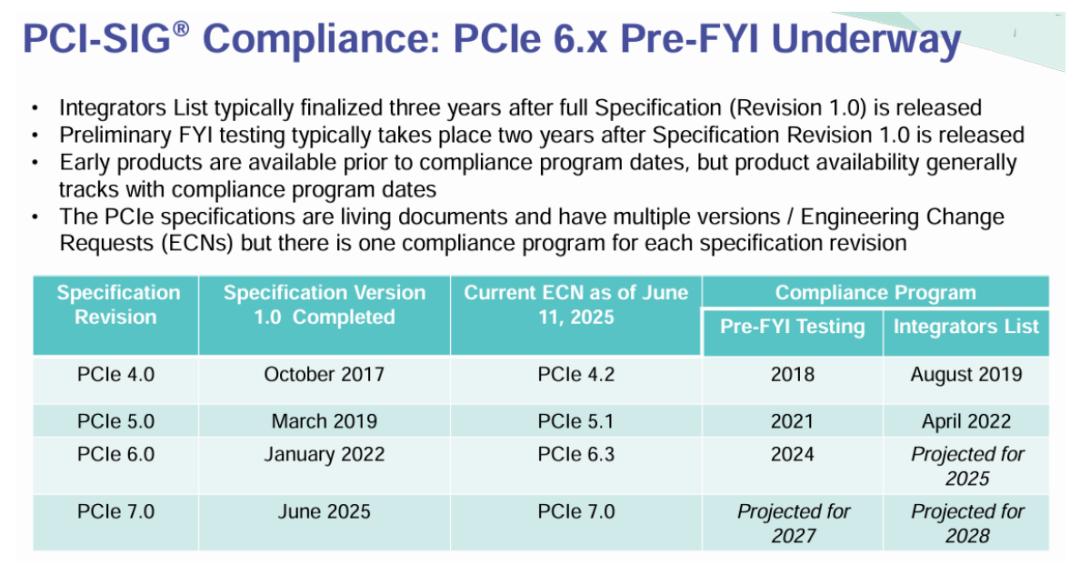

依據PCI-SIG規劃,該規范將在草案階段要點優化信道參數與能效水平,正本規范于2025年完結擬定,將于2027年完結預發布測驗 (Pre-FYI)。

圖源:PCI-SIG官網

值得重視的是,PCIe 7.0有望引進光學銜接計劃以增強長間隔傳輸功能,而職業普遍認為其全面遍及或將推延至2028年左右。這一晉級將為高速互聯技能注入新動能,繼續支撐數據密集型場景的開展需求。

除了發布規范之外,PCI-SIG 還宣告了新的光纖互連規范修訂,以完結更高的PCIe技能功能。“光學感知重定時器工程改變告訴 (ECN)”修訂了PCIe 6.4規范和新的PCIe 7.0規范,納入了依據PCIe重定時器的處理計劃,然后供給了首個經過光纖完結PCIe技能的職業規范化辦法。估計該技能將首要運用于人工智能/機器學習和云等數據中心運用,一起跟著PCIe技能逐步遍及,估計很多細分商場將呈現立異用例。

在高速數據傳輸和核算需求日益增加的今日,PCIe 正在閱歷一場史無前例的光互聯改造。半導體職業調查此前文章《PCIe,新改造》中對此有詳細描繪,在此不再贅述。

PCIe 8.0:繼續接連帶寬翻倍傳統

2025年8月,PCI-SIG協會宣告正在開發的PCIe 8.0規范將把數據速率進步至256GT/s,相較PCIe 7.0再度完結翻倍,并計劃于2028年向會員發布。經過x16通道裝備,PCIe 8.0的雙向帶寬將到達1TB/s,為高帶寬核算場景帶來史無前例的功能空間。

圖源:PCI-SIG官網

依據PCI-SIG的闡明,PCIe 8.0規范在功能進步的一起,將繼續堅持向后兼容性并滿意低推延、可靠性和功耗優化的規劃方針。要害特性包含:

256.0 GT/s原始比特率,x16裝備完結1 TB/s雙向傳輸速率

引進新的銜接器技能,滿意更高信號完好性需求

優化推延與FEC(前向糾錯)機制,保證可靠性

增強協議功能以進步有用帶寬利用率

繼續下降功耗,滿意綠色數據中心與移動核算需求

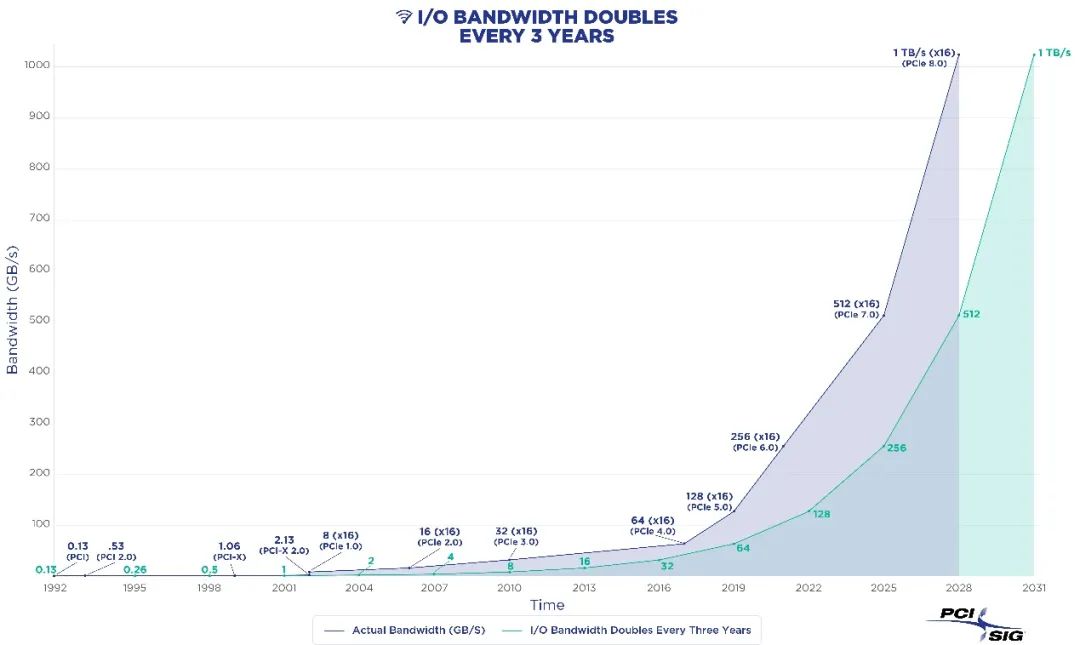

依據PCI-SIG發布的速率開展趨勢能看到,PCIe規范均勻每三到四年完結一次速度翻倍迭代。在PCIe 7.0到8.0的躍遷中,通道信號質量、走線規劃和封裝資料都將面對新的應戰。

未來,PCIe 8.0或許推進以下技能開展方向:

先進封裝與芯片間互連:協同規劃將成為高功能核算渠道的中心競賽力。

光互連技能:在更高傳輸速率下,電信號完好性受限,光互連或將在PCIe 9.0乃至更早的擴展中引進。

體系功耗優化:數據中心對能效的苛刻要求將促進PCIe協議繼續迭代低功耗特性。

PCIe的商場解析與優勢圖譜

(PCIe1.0-8.0的帶寬比照表格 圖源:PCI-SIG官網)

在曩昔二十多年中,PCIe技能一直是高功能、低推延I/O銜接的首選處理計劃。從1.0的2.5 GT/s到7.0的128 GT/s,再到8.0的256 GT/s,PCIe簡直每一代都將速率翻倍,顯示出技能開展的迅猛速度。

這一趨勢的背面,是核算需求的繼續迸發,也反映出PCIe技能對高功能核算、數據傳輸需求繼續增加的支撐效果。

AI/ML練習與推理:大模型練習已打破數千億參數規劃,GPU、AI加快卡和存儲體系的互連需求激增。

高速網絡與邊際核算:低推延傳輸和海量數據處理要求更高的I/O帶寬支撐。

量子核算與HPC:需求高吞吐、低推延的體系級互連架構。

轎車與國防范疇:自動駕駛和航空電子對實時性和可靠性的要求使高速總線規范成為要害組件。

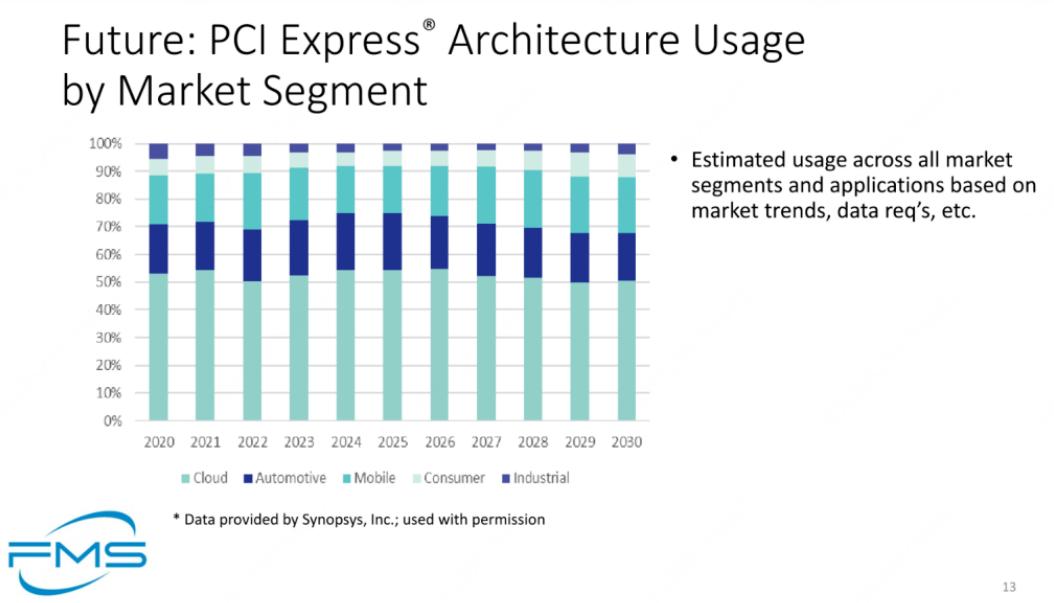

從運用商場來看,PCle在多個職業場景中有著不同的運用狀況。云核算范疇占有最大比例(超越50%),估計將繼續主導PCle架構在數據中心和服務器范疇的運用商場;在轎車商場中,PCle的選用率自2020年起穩步上升,這是因為轎車職業對AI和ADAS需求增加所造成的;移動設備商場中,PCle的商場比例穩定在10%-20%左右,首要用于智能設備和高效互聯技能;消費類電子商場里,PCle的比例逐步擴展,在家庭設備和個人電腦中繼續得到運用;而在工業范疇,跟著工業自動化和IoT的開展,PCle的選用率呈緩慢增加趨勢,其重要性日益凸顯。

圖源:FMS

詳細來看,PCIe接口憑仗其高帶寬和低推延的特性,被廣泛運用于各類核算設備中:

圖形處理器(GPU): PCIe接口用于銜接高功能GPU,為圖形烘托、人工智能練習等使命供給高速數據傳輸通道;

CPU與主板芯片組通訊:CPU處理器經過PCIe通道與主板南橋芯片(PCH)銜接,操控周邊設備(如USB、SATA接口);

固態硬盤(SSD): PCIe接口被廣泛用于NVMe SSD,明顯進步了存儲設備的讀寫速度;

網絡接口卡(NIC): 高帶寬的網絡接口卡一般選用PCIe接口,保證數據傳輸的高效性;

高功能核算(HPC): 在HPC體系中,PCIe接口用于銜接不同核算節點和存儲設備,以完結數據的高速傳輸。

不難理解,PCIe作為廣泛選用的芯片間互聯協議,其架構優勢在于削減了互操作性應戰。谁有财色无边全文无删减這一特性有助于用戶完結異構核算,行將CPU、GPU和AI加快器進行結合,經過規范化的互聯技能,極大地進步了異構核算的功率和功能。

尤其是在對 AI 技能的支撐方面,PCIe具有高帶寬、低推延和兼容性的特色,這些特性使其成為支撐AI技能廣泛布置和增加的重要柱石。其前向和后向兼容性協助決策者在布置AI技能時進步靈敏性,可以有用縮短布置周期,而且下降布置危險,這使得PCIe在AI職業的選用率將會很高。

依據此,有相關數據猜測,到2030年,PCIe技能在AI商場(包括邊際AI和數據中心AI)的總可用商場估計可達27.84億美元,年均復合增加率為22%。其間,邊際AI商場估計將以50%的年均復合增加率快速增加,這是因為企業不斷布置邊際服務器且AI技能日益遍及。

PCIe應戰與競合:專用技能沖擊下的包圍之路

PCIe接口從2001年開展至今,在協議的完好性上現已樹立足夠高的“護城河”。

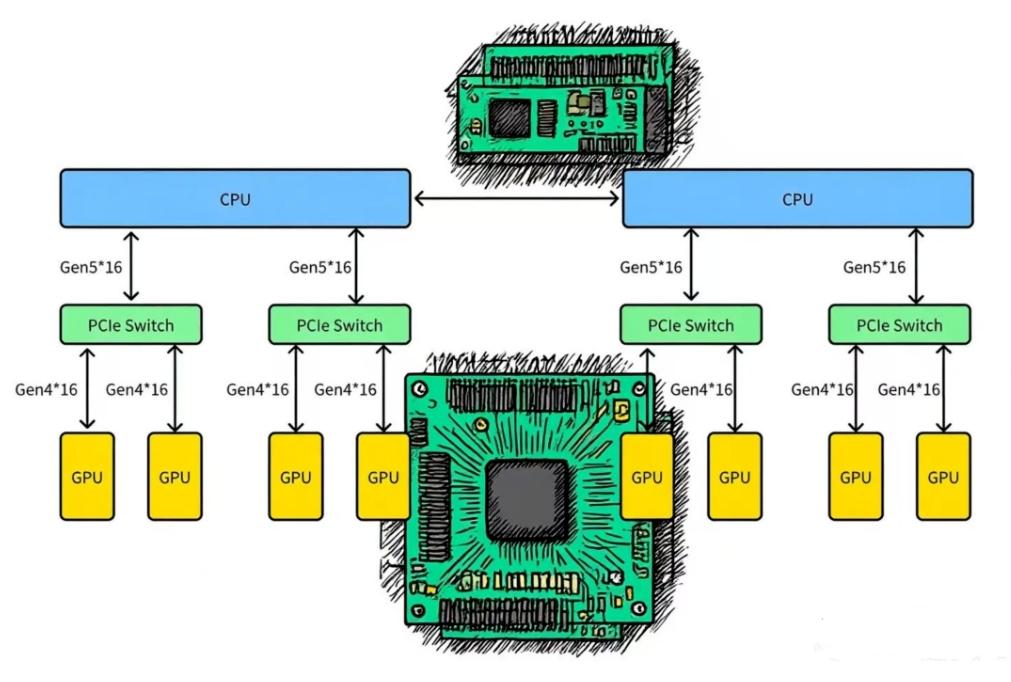

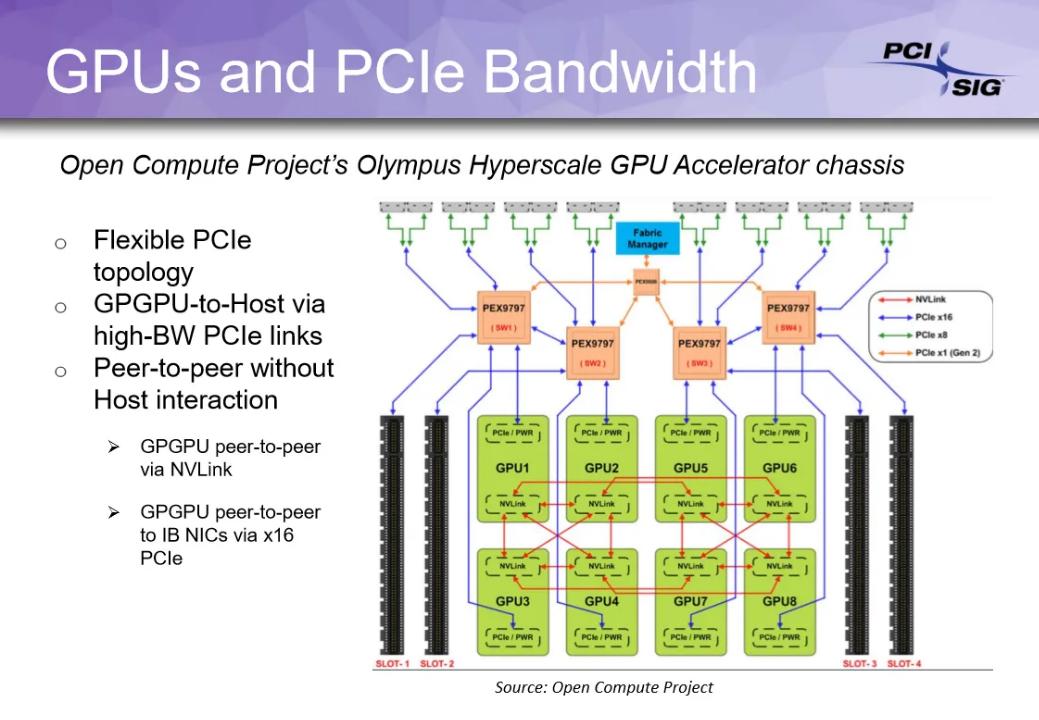

但跟著職業不斷演進,在GPU卡間互聯體系中,PCIe作為傳統互聯接口正面對明顯應戰。該體系選用CPU與GPU別離的架構,CPU擔任使命調度,GPU專心并行核算,而處理器間的互聯帶寬和拓撲結構直接影響功能發揮。

傳統架構中,GPU經過PCIe銜接CPU導致無法直接點對點通訊,且CPU供給的PCIe通道數量約束了GPU擴展;即使憑借PCIe Switch完結多GPU接入和P2P通訊,跟著GPU占比攀升,PCIe帶寬遠低于處理器與本地內存的帶寬,逐步成為體系功能瓶頸。

為打破這一約束,英偉達和AMD別離推出NVLink、Infinity Fabric等面向GPU的高速互聯技能,經過更高帶寬和更低推延進步數據傳輸功率,支撐大規劃GPU集群構建,充沛開釋核算潛力。但此類技能歸于廠商私有計劃,難以跨渠道適配其他GPU場景,存在生態封閉性約束,也推進了敞開異構智能加快體系的探究。

在此布景下,2024年5月由Google、Meta、微軟、AMD、Intel等科技巨子聯合建立的UALink(Ultra Accelerator Link)聯盟應運而生。該聯盟致力于開發敞開的職業規范,聚集AI數據中心GPU網絡通訊優化,旨在打破英偉達在該范疇的主導位置,經過會聚職業力氣供給更高效、靈敏的跨渠道處理計劃,呼應人工智能對高速數據傳輸的火急需求,推進技能合作與立異開展。

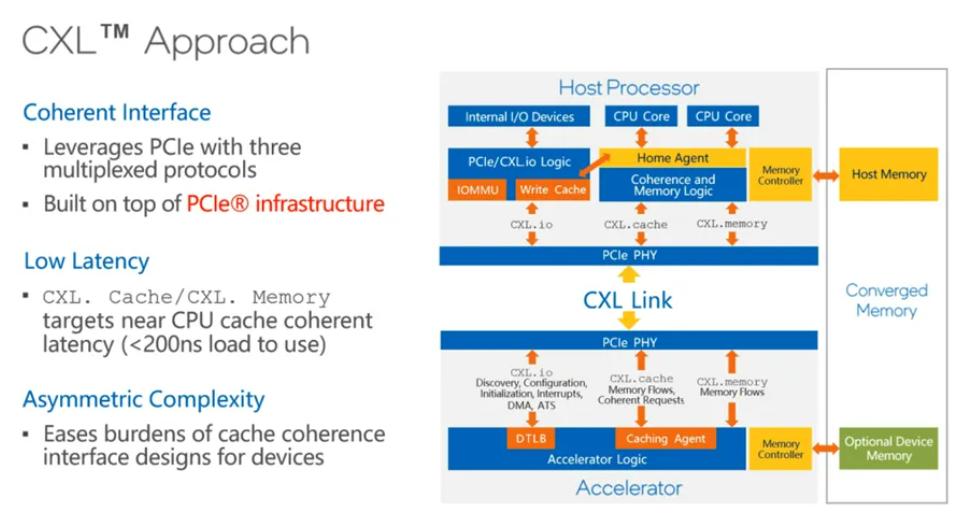

此外,在PCIe面對NVLink等專用互聯技能沖擊、帶寬瓶頸逐步凸顯的趨勢下,Intel早在2019年3月還推出了CXL(Compute Express Link)協議接口,為高功能異構核算場景供給新的互聯處理計劃。

CXL選用“兼容演進”戰略,將協議封裝于PCIe鏈路層數據包中傳輸,在CPU端的PCIe總控后端經過業務標識分流CXL專屬業務至專門處理邏輯,完結了與PCIe 5.0接口規范的兼容,可直接在PCIe 5.0架構上運轉,既接連了PCIe的硬件生態根底,又進一步穩固了其在核算機體系中的中心影響力。

該協議的中心方針是完結CPU與GPU、FPGA及其他加快器之間的高速高效互聯,滿意異構核算對低推延、高帶寬數據交互的需求。從生態布局來看,Intel經過構建這一通往內存的“高速路”,企圖在GPU、DPU等加快設備的互聯中把握主導權——例如第四代英特爾至強可擴展處理器最多支撐4個CXL設備,兼容CXL Type1和Type2類型,經過設備接入數量與類型的操控形成對加快設備的制衡。現在NVIDIA等廠商也已參加CXL聯盟,這一敞開協議不只為內存密集型和IO密集型場景供給更高功能價值,更成為Intel在高速互聯范疇應對技能應戰、平衡職業生態的要害布局。

在AI年代網絡互聯技能的選型中,PCIe、NVLink、CXL等計劃的挑選成為職業重視的焦點。

不過,這一挑選并非單一技能好壞的判別,而是需求結合多重維度歸納考量,未來技能格式的演化不只依賴于技能立異的打破,更受商場需求導向與職業協作生態的深刻影響。關于企業而言,在AI網絡互聯的技能選擇中,需依據本身對功能指標、本錢操控、運用場景適配及長時間開展兼容性的歸納評價,才能在動態改變的技能浪潮中找到最適合的途徑。

寫在最終

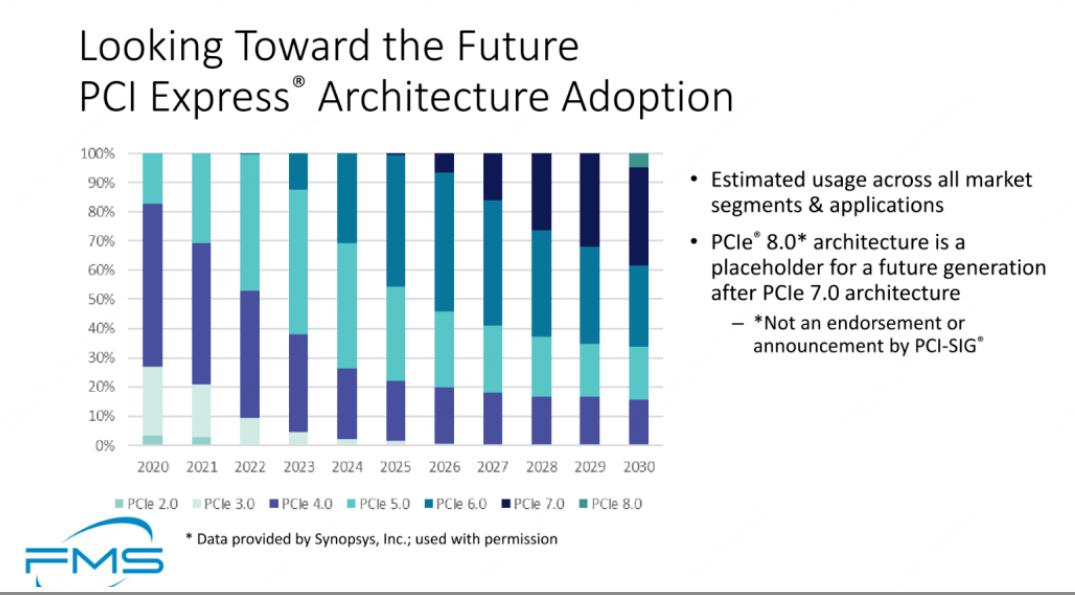

現在數據中心中廣泛運用的代次是PCIe 5.0和PCIe 6.0;2027年后PCIe 7.0或將開端大規劃選用,逐步遍及并頂替前代規范;PCIe 8.0的規劃化運用估計呈現在2030年今后,將進一步進步帶寬和傳輸功能。

圖源:FMS

那么,PCIe傳輸速率每代次翻倍,是否具有可繼續性?

對此有專家表明,盡管PCIe傳輸速率每代次翻倍的趨勢盡管已繼續了很多年,但其可繼續性逐步面對多方面的應戰。從技能和物理層面來看,這一增加趨勢并非無限繼續。假如要保證傳輸速率的繼續增加,還將在許多技能方面發揮重要效果,例如:

先進信號調制,例如選用的PAM4調制技能,在未來或許進一步優化或引進更雜亂的信號編碼。

光互連技能代替銅線傳輸的部分約束,光纖互連可完結更高帶寬和更低功耗。

封裝與資料立異經過改善主板布線、半導體資料和封裝技能,削減信號損耗。

更高效的過錯糾錯技能優化FEC和CRC等技能,下降高速傳輸的誤碼率。

展望未來,PCIe技能的速率演進將深度餞別“光-電協同、軟硬結合、場景泛化”的開展邏輯。從PCIe 8.0完結256 GT/s的帶寬打破,到更久遠的技能迭代,其間心打破途徑明晰可辨:經過光互連技能打破電信號傳輸的物理瓶頸,依托協議架構立異進步傳輸功率,憑借智能化調度優化資源分配。這種多維協同的技能道路,旨在高速率、低推延、高可靠性與本錢效益之間構建精準平衡。

作為支撐數字根底設施的中心互聯技能,PCIe不只將繼續穩固在通用核算范疇的柱石位置,更將成為AI練習集群、量子-經典混合核算等前沿場景的“數字高速公路”。其敞開生態與繼續進化才能,將為數字經濟的規劃化立異供給堅實的技能底座,推進核算架構向更高效、更靈敏、更具擴展性的未來演進。

*免責聲明:本文由作者原創。文章內容系作者個人觀念,半導體職業調查轉載僅為了傳達一種不同的觀念,不代表半導體職業調查對該觀念附和或支撐,假如有任何貳言,歡迎聯絡半導體職業調查。

本文來自微信大眾號 “半導體職業調查”(ID:icbank),作者:L晨光,36氪經授權發布。